等精度频率计的规划与验证

文章摘要:凭借于QuartusII PLL_IP核发生一个恣意频率被测时钟信号,规划一个等精度丈量模块,经过其处理后,再数码管上显现出六位的丈量频率数值,验证丈量的准确度。

关键词:Verilog HDL;等精度频率丈量;数码管;PLL_IP核

终究框图:

频率计,即频率计数器,专用于丈量被测信号频率,根本作业原理便是当被测信号在特定时刻段T内的周期个数为N时,则被测信号的频率freq能够经过公式freq=N/T核算得出。

在EDA规划中,常见的频率丈量方法包含频率丈量法(合适高频被测信号)、周期丈量法(合适低频被测信号)和等精度丈量法。频率丈量法是经过核算单位时刻内上升沿(或下降沿等)来核算频率,而周期丈量法是经过丈量上升沿(或下降沿等)的时刻距离来核算频率。等精度丈量法与前两种不同,其在于门控时刻的设定。

【根底原理】

在等精度丈量法中,门控时刻的长度并非固定,而会依据被测时钟信号的周期进行调整,确保其为被测时钟信号周期的整数倍。在这样的参阅门限规模内,一起记载规范时钟和被测时钟信号的周期数,随后经过核算两者的比例关系,得到被测信号的时钟频率。

预先设定一个软件门限,在此门限划定丈量参阅规模,经过对丈量信号Measured_sig上升沿触发,可得到一个相对的参阅门限REF_threshold,其是被测时钟周期的整数倍,消除了被测信号存在的±1个时钟周期差错。

丈量方法:

参阅门限规模内,计数被测信号周期个数为N;给一个高频(固定频率Fs)规范信号,并计数得到其在相同门限下周期个数为Y;凭借 N * 1 / Fn = Y * 1/Fs 可知被测信号频率 Fn = Fs * N / Y。

f为被测信号频率的丈量值,f'为实践频率,参阅门限T;

丈量差错β = | f'-f | / f' * 100%,若疏忽规范信号的差错,可得到f' = N / (Y ± ΔY)* Fs;

联立得到 β = ΔY/Y *100% ≤ 1/Y = 1/(Fs * T)

定论:被测信号的频率挨近或高于规范信号,丈量的差错会大,便是说,增大规范信号频率,或许扩展软件门限,这样可进步丈量精度。

【时序逻辑规划】

体系时钟sys_clk为50Mhz信号,sys_rst为体系复位。被测信号Measured_sig设定恣意频率,thres_cnt门限计数周期定位1.5s(可调),前0.25s为信号坚持,在中心的1.00s内是软件门限丈量规模,后0.25s为核算时刻。actual_thres是参阅门限规模,也便是被测信号的实践丈量规模,是被测时钟周期的整数倍。

meas_clk_cnt到act_cnt_reg是被测时钟信号相对于参阅门限的周期个数丈量,终究得到计数N。由被测时钟信号上升沿触发,act_thres_reg对actual_thres做了一个拖延坚持(打拍),得到计数完毕信号act_reg_flag,经过其高电平触发计数值搬运值act_cnt_reg坚持。std_clk_cnt到std_cnt_reg原理相同如此,是规范高频信号相对于参阅门限的周期个数丈量,终究得到计数Y,经过公式核算得到被测信号频率。

对上述时序图中的信号,编写Verilog程序:(留意不同的信号触发类型)

parameter THRES_CNT_MAX = 27'd75_000_000;

parameter THRES_CNT_250MS = 27'd12_500_000;

parameter CNT_STAND_FREP = 27'd100_000_000;

assign Std_flag = (Std_reg)&&(!act_thres)?1'b1:1'b0;

assign act_reg_flag = (act_thres_reg)&&(!act_thres)?1'b1:1'b0;

always @(posedge sys_clk or negedge sys_rst)begin

if(!sys_rst) thres_cnt <= 27'd0;

else if(thres_cnt == THRES_CNT_MAX -1'b1) thres_cnt <= 27'd0;

else thres_cnt <= thres_cnt + 1'b1;

end

always @(posedge sys_clk or negedge sys_rst)begin

if(!sys_rst) thres_range <= 1'b0;

else if((thres_cnt > (THRES_CNT_250MS-1'b1))&&(thres_cnt < (THRES_CNT_MAX-THRES_CNT_250MS-1'b1))) thres_range <= 1'b1;

else thres_range <= 1'b0;

end

always @(posedge measured_sig or negedge sys_rst)begin

if(!sys_rst) act_thres <= 1'b0;

else act_thres <= thres_range;

end

always @(posedge measured_sig or negedge sys_rst)begin

if(!sys_rst) meas_clk_cnt <= 48'd0;

else if(!act_thres) meas_clk_cnt <= 48'd0;

else meas_clk_cnt <= meas_clk_cnt + 1'b1;

end

always @(posedge measured_sig or negedge sys_rst)begin

if(!sys_rst) act_thres_reg <= 1'b0;

else act_thres_reg <= act_thres;

end

always @(posedge measured_sig or negedge sys_rst)begin

if(!sys_rst)act_cnt_reg <= 48'd0;

else if(act_reg_flag) act_cnt_reg <= meas_clk_cnt;

end

always @(posedge clk_stand or negedge sys_rst)begin

if(!sys_rst) std_clk_cnt <= 48'd0;

else if(!act_thres)std_clk_cnt <= 48'd0;

else std_clk_cnt <= std_clk_cnt + 1'b1;

end

always @(posedge clk_stand or negedge sys_rst)begin

if(!sys_rst) Std_reg <= 1'd0;

else Std_reg <= act_thres;

end

always @(posedge clk_stand or negedge sys_rst)begin

if(!sys_rst) std_cnt_reg <= 48'd0;

else if(Std_flag) std_cnt_reg <= std_clk_cnt;

end

always @(posedge sys_clk or negedge sys_rst)begin

if(!sys_rst) calc_flag <= 1'd0;

else if(thres_cnt == THRES_CNT_MAX-1)calc_flag <= 1'd1;

else calc_flag <= 1'd0;

end

always @(posedge sys_clk or negedge sys_rst)begin

if(!sys_rst)frep_result <= 32'd0;

else if(calc_flag)frep_result <= (CNT_STAND_FREP/ std_cnt_reg* act_cnt_reg);

end

其间的规范高频信号clk_stand需求凭借于QuartusII的PLL_IP核发生,模块实例化其间。

//Stand_clk from PLL_IP_core

clk_stand clk_stand_inst (

.areset ( !sys_rst ),//Hign Level take effect

.inclk0 ( sys_clk ),

.c0 ( clk_stand ) );

【频测模块仿真验证】

在仿真程序及仿真现象中,设定体系时钟20ns,即50Mhz,而被测时钟周期216ns,即1 / 216 * 10e9 ≈ 4.6296Mhz。而且,为便利调查波形改变,将软件门限缩小了10e5倍(精度减小),终究得到被测信号频率 32'h46a806 ≈ 4.6305Mhz,差错0.9khz,仿真上的时序改变均达到时序逻辑要求。

always #10 sys_clk =~sys_clk;

always #108 clk_test =~clk_test;

defparam frep_calc_inst.THRES_CNT_MAX = 750;

defparam frep_calc_inst.THRES_CNT_250MS = 125;

【布置其他模块】

考虑到最后的板级验证,没有信号源和示波器经过,在此再树立一个PLL_IP核发生一个“恣意时钟信号”,作为被测信号,而且将终究的成果输入到六位数码管上显现出来调查,该被测信号的实践频率为3.580097Mhz。

其次,实例化数码管显现模块,这儿仍是存在问题的,测信号的实践频率十六进制显现选用六位即可,这儿图个便利,用assign直接赋值了。

digital digital_inst(

.sys_clk (sys_clk ),

.sys_rst (sys_rst ),

.clk_2khz (clk_2khz ),

.num6 (num6 ), //assign num6 = frep_result[23:20];

.num5 (num5 ), //assign num5 = frep_result[19:16];

.num4 (num4 ), //......

.num3 (num3 ),

.num2 (num2 ),

.num1 (num1 ),

.sel_cnt (sel_cnt ), //所运用到的位数

.dp_cnt (dp_cnt ), //小数点所在位号

.seg_sel (seg_sel ), //数码管位选

.seg_led (seg_led ) //数码管段选

);

【板级验证计划】

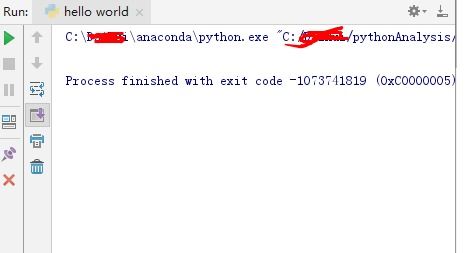

从下图能够看到,代码里选用了除法运算。在FPGA或ASIC规划中,除法运算自身是一种杂乱的算术操作,比较于加法、减法和乘法,它需求更多的核算过程和逻辑单元来完结,除法操作往往需求专门的硬件除法器。

上机测验后,烧录至EP4CE10F17C8开发板,数码管显现十六进制36A0C1,刚好是3,580,097hz。软件门限规模为1.00s,规范信号设定100Mhz,丈量准确度仍是比较高的。

文献参阅:

[1]根据Altera EP4CE10 征程Mini开发板文档(https://doc.embedfire.com/fpga/altera/ep4ce10_mini/zh/latest/fpga/Frequency_Meter.html)

[2]王立华,周松江,高世皓,等. 根据内嵌Cortex-M3内核FPGA的等精度频率计规划[J]. 实验室研讨与探究,2017,36(7):139-143,181. DOI:10.3969/j.issn.1006-7167.2017.07.033.

本篇文章中运用的Verilog程序模块,若有需见网页左栏Gitee库房链接:https://gitee.com/silly-big-head/little-mouse-funnyhouse/tree/FPGA-Verilog/